DINI Group Announces the DNPCIE_80G_A10_LL, an Intel/Altera Arria-10 FPGA Board for Low Latency Network Applications and Data Cent Algorithmic Acceleration

La Jolla, CA, October 20, 2016 --(PR.com)-- DINI Group announces the immediate availability of the DNPCIE_80G_A10_LL an Intel/Altera Arria-10 FPGA board with a capacity of 10 million ASIC gates. This product is optimized for custom network applications such as inline packet processing using TOE (TCP/IP Offload) and line speed algorithmic trading. The DNPCIE_80G_A10_LL joins a long list of FPGA-based network-targeted products from DINI Group, the industry’s established leader in large FPGA platforms.

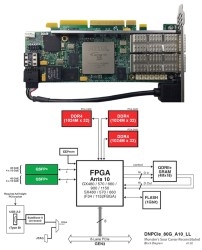

The DNPCIE_80G_A10 is a half-height PCIe board with a single Arria-10 FPGA, three banks of DDR4 memory, and a single bank of QDRII+ memory.

For the FPGA, the DNPCIE_80G_A10_LL employs the high I/O-count, 1152-pin, flip-chip F34 BGA package. The Arria- 10 family of FPGAs contains high-speed transceivers capable of 12.5Gb/s without the need for an external PHY. Eight of these transceivers are used for an 8-lane GEN3 PCIe interface. Two sets of four of the high-speed transceivers are connected to QSFP+ sockets for two 40GbE Ethernet ports or up to 8 channels of 10 GbE.

One of seven possible Arria-10 FPGAs can be stuffed (largest to smallest): GX1150, GX900, GX660, GX570, GX480, GX320, GX270. The SX variation that contains the embedded Dual-core ARM® Cortex®-A9 MPCoreTM processor is also an option. Those device options are SX660, SX570, SX480, SX320, SX270. Several IEEE 754 floating point functions can be implemented using the DSP blocks in the FPGA fabric.

The DNPCIE_80G_A10_LL supports three independent DDR4 banks each of 4GB in size. Each bank is PC2400 with a 1024M x 32 configuration. For data lookup that requires absolute minimum latency, the DNPCIE_80G_A10_LL hosts a QDRII+ memory structured as 4Mx18.

“We made this new Arria-10 board as fast and as versatile as possible,” says Mike Dini, president, “It is perfectly suited for cluster deployment in co-location spaces or exchanges. Network applications and High Frequency/Low Latency Algorithmic Trading can enjoy line speed communications and packet processing with this little jewel.”

The DNPCIE_80G_A10 is a half-height PCIe board with a single Arria-10 FPGA, three banks of DDR4 memory, and a single bank of QDRII+ memory.

For the FPGA, the DNPCIE_80G_A10_LL employs the high I/O-count, 1152-pin, flip-chip F34 BGA package. The Arria- 10 family of FPGAs contains high-speed transceivers capable of 12.5Gb/s without the need for an external PHY. Eight of these transceivers are used for an 8-lane GEN3 PCIe interface. Two sets of four of the high-speed transceivers are connected to QSFP+ sockets for two 40GbE Ethernet ports or up to 8 channels of 10 GbE.

One of seven possible Arria-10 FPGAs can be stuffed (largest to smallest): GX1150, GX900, GX660, GX570, GX480, GX320, GX270. The SX variation that contains the embedded Dual-core ARM® Cortex®-A9 MPCoreTM processor is also an option. Those device options are SX660, SX570, SX480, SX320, SX270. Several IEEE 754 floating point functions can be implemented using the DSP blocks in the FPGA fabric.

The DNPCIE_80G_A10_LL supports three independent DDR4 banks each of 4GB in size. Each bank is PC2400 with a 1024M x 32 configuration. For data lookup that requires absolute minimum latency, the DNPCIE_80G_A10_LL hosts a QDRII+ memory structured as 4Mx18.

“We made this new Arria-10 board as fast and as versatile as possible,” says Mike Dini, president, “It is perfectly suited for cluster deployment in co-location spaces or exchanges. Network applications and High Frequency/Low Latency Algorithmic Trading can enjoy line speed communications and packet processing with this little jewel.”

Contact

Dini Group

Mike Dini

858 454 3419 x11

www.dinigroup.com

Mike Dini

858 454 3419 x11

www.dinigroup.com

Multimedia

DNPCIE_80G_A10_LL Press Release (.pdf)

Full press release for the DNPCIE_80G_A10_LL.

Categories